Ëmfaassend Guide fir DS1302 RTC

2024-11-09

5485

Den DS1302 Chip Seamlos integréiert eng Echtzäit Auer / Kalenner System an 31 Bytes vu statesche Ram, déi gnädeg Ofpersiere vun der Tëschenzäit vun der Tëschenzäit ass.Et bitt e Mëttel fir effektiv ze kommunizéieren mat Mikroprozessioun duerch eng vereinfacht Serien Interface ze notzen.Dëst Dokument ventures déif an de Chip d'Architektur, entdeckt déi komplizéiert Aarbecht an den Danz vun Elektronen an seng Circuiten.Et erwächt d'Virwëtzegkeet vun deenen déi an der Eleganz vum technesche Design intresséiert sinn.

Calalog

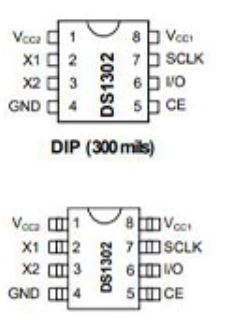

DS1302 PIN Verbindungen Iwwersiicht

CAD Modell vun DS1302

Iwwersiicht vun DS1302

The DS1302 kombinéiert eng Echtzäit Auer / Kalenner mat 31 Bytes vu statesche Ram, verstoppt fir d'Léif-Kraaft Szenarie ze passen.Et bitt bedeckt TimeAxat Informatioune, Minutten, Stonnen, Stonnen, Datumen, a Joer, komplett am Leed kréien deene wesentlech Upassung gerecht gëtt.Dëse System erlaabt Iech souwuel 24-Stonn an 12 Stonne Formateure, mat engem AM / PM Indikator mat den digitale Zäitpräten ze këllen.Seng Serien Kommunikatiounsinface Staffassivitéit Konnektivitéit mat Divere Mikrocrozesser, Emissioun Adaptabilitéit am System Design.

Features vun DS1302

Integréiert Timekeeping an Daten Ëmgang

Den DS1302 beweist eng gutt ofgerënnt Optioun fir den Timespinging Aufgaben, ëmfaassen all Operatiounen, wärend eng temporär Datenlagerungen a sengem Ram ze bidden.Den Timekeeping ass effizient effizient iwwer eng gestreckt dräi-wirhafte Serien Interface, aktivéiert glat Kommunikatioun mat Mikrokontroller.Dëse Setup huet divers Datendransfermethoden ugewisen, sou wéi eenzeg-Byte an de Burstmodus, injektioun vun der flexiver Systemer.

Effizient Energie benotzt

Eng notable Charakteristik vun den DS1302 ass seng prudent Power Notzung, an enger Sprosspréch vun 2,0V bis 5,5v.Wann Dir op 2,02 Operatioun benotzt, benotzt se nëmmen 33a, huelt weiderden eng gutt schaarf Wiel fir niddereg-Kraaft Uwendungen wéi d'Batterie.Dësen Niveau vun Energieschterer Effizienz ass d'Frequenz vun der Batterie verännert, verännert sech d'Liewensquote vum normale Faktor fir Remote Setups ze managen, déi Zouloossung a manner Ënnerbriechungen a manner Ënnerbriechunge maachen.

Space-wirtschaftlech Design

The DS1302's compact 8-pin DIP and SO packages ensure it takes up minimal space, an attractive trait in the design of devices where every bit of space is invaluable.De Selbstof säi Resultat war awer an de Formatsofgank ze an der Wäertercorten, aus Verbraucher Elektrechter fir Industriminine fir Industrien.Diséinten, ass de klenge Match z'esinn duerch de Schüchtungen vum Chip an enger Circuit Design ze maachen, wat se méi héich bleif sinn ze kréien.

Breet Betrib Temperaturbereich

Den DS1302's Kapazitéit fir zouverlässeg bannent enger industrieller Temperaturpabeieren, déi en Euro erëmfonnt huet, da gëtt et anscheinend designt.Dëse Trait mécht et eng ofhängeg Wiel fir Geräter déi stänneg an extremem Temperaturen ze maachen, sou wéi déi an Outdoor Astellungen an Automotiv Uwendungen.Déi robustemperatur Temperatur Toleranz steet als Testament fir seng ongewollten Zouverlächen, e Verdauung, wat staark Plaz an der Missiounsaz.

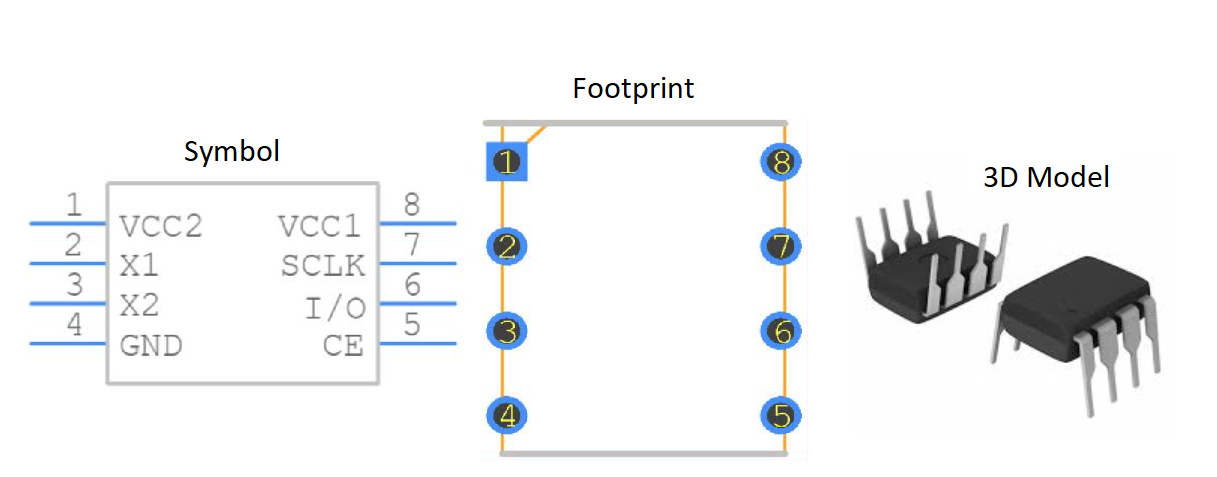

DS1302 Fonctionnaire Block Diagramm

Technesch Spezifikatioune

Maximim integréiert eng lafe Spektrum vu Spezifikatioune fir den DS130-Add, Serverätzen ze deelen, an Invalscht ze halen.The DS1302 + Ausgänzend an präzisim Timing Funktionalitéit, en Aspekt fir Systemer déi sech op metikuléiser Zäitdäckung an effizient Datesaurantement.Den Tabelle hei hei ënner ass d'technesche Spezifiziounen, Zousteie, Parameteren vum Maximd integréierten DS1302 +.

|

Tipps |

Paramesnéiergank |

|

Fabréck Leadzäit |

9 Wochen |

|

Mont |

Duerch Lach |

|

Package / Fall |

8-Dip (0,300, 7.62mm)

|

|

Gewun Du |

930.001806MG |

|

Verpackungen |

Tubédominie |

|

Jwd-609 Code |

EXT EX |

|

Deellizist |

Aktiv Säit |

|

Zuel vun den Terminatiounen |

8 |

|

Tipps |

Auer / Kalenner |

|

Verrossung - Offer |

2v ~ 5.5V |

|

Peak Reflow Temperatur (CEL) |

260 |

|

Terminal Pitch |

2.44M |

|

Basebala Deel Zuel |

DS1302 |

|

Zuel vun den Ausgaben |

1 |

|

Power Reserven |

3 / 5V |

|

Gedächtnisgréisst |

31b |

|

Auer Frequenz |

0.032mhz |

|

Aswéier formënnformat |

Hh: mm: ss (12/24 hr) |

|

Aktuell - Timekeeping (Max) |

0,3μμa ~ 1μa @ 2v ~ 5v |

|

Ënnerbriechung Fäegkeet |

N |

|

Framtlwer |

JO |

|

FONTassementer |

Sprangjoer, NVSRAM, Trickle-Ladeger |

|

Läitheet |

9.98MMM |

|

Erreechen svhc |

Keen svhc |

|

Rohs Status |

Rohs3 kompatibel |

|

Kontakt schlift |

Tinn |

|

Montéierend Typ |

Duerch Lach |

|

Zuel vun de Pinnen |

8 |

|

Betribsortemperatur |

0 ° C ~ 70 ° C |

|

Verëffentlecht |

Jo |

|

PBFree Code |

Jo |

|

Fiichtegkeet Sensibilitéitsniveau (MSL) |

1 (onlimitéiert) |

|

Eccn Code |

Ouer99 |

|

Zousätzlech Feature |

Burst Modus Ram Datentransfer;Timesheeping

Aktuell = 0.3μa |

|

Terminal Positioun |

Dueblieder |

|

Liwwerreibei |

3.3V |

|

Zäit @ Peak Reflow Temperatur-Max (en) |

30 |

|

Pin Ziel |

8 |

|

Betrage Versuergungspannung |

3.3V |

|

Interzäit |

3-Wire Serial |

|

Betribsbitt et aktueller Betrib |

1.2MA |

|

Logesch Funktioun |

Wopp |

|

Datum Format |

Yy-mm-dd-dd |

|

Zäit-m |

Sekonnen |

|

Liwweren Spannung - Versuergung, Batterie |

2v ~ 5.5V |

|

Informatioun Zouganksmethod |

Seriell, 3-Drot |

|

Héicht |

4.46mm |

|

Breet |

7.87MM |

|

Stralung Hardening |

Nee |

|

Stras |

Stras |

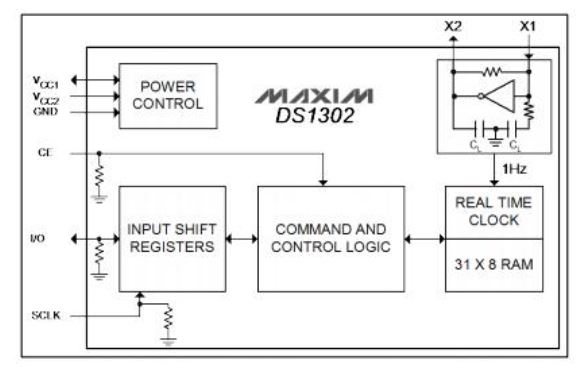

Betrib Circuit vun DS1302

Den DS1302 Real-Zäit Clock Module verbënnt mat Mikroprozessioun duerch eng synchronesch Seriun Commercount Interface, erfuerderlech just dräi Verbindungen: Chips / Out), an Serien.Dëst streamlined wirhafte Frame gëtt fir seng Einfachheet an Zouverlässegkeet appréciéiert, spigelen d'Wonsch no Segment am Design.Datentransfer op an aus der Auer / RAM kann entweder ee Byt op enger Zäit oder a Bursts vu bis zu 31 Bytes sinn.Den Design erméiglecht op extrem niddreg Kraaft, behalen Daten an Auer Informatiounen iwwer manner wéi 1 μw.Den Typent Ordurs Cagnier gëtt ënnert "gewisen.

Alternativen fir DS1302

|

Deelnummer |

Broessdatsch |

Hiersteller |

|

DS1202n |

Real Zäit Auer, fläisseg, 0 Timer (en),

Cmos, Pdip8 |

Dallas semiconduction |

|

DS1202 |

Real Zäit Auer, fläisseg, 0 Timer (en),

Cmos, Pdip8 |

Dallas semiconduction |

|

DS1302n + |

Real Zäit Auer, CMOS, PDIP8, Dip-8 |

Cypress Semiconductuctor |

|

DS1302n |

Real Zäit Auer, fläisseg, 0 Timer (en),

CMOS, PDIP8, 0.300 Zoll, Plastik, Daucht-8 |

Maxim integréiert Produkter |

|

DS1302 |

Real Zäit Auer, fläisseg, 0 Timer (en),

CMOS, PDIP8, 0,300 Zoll, Dip-8 |

Dallas semiconduction |

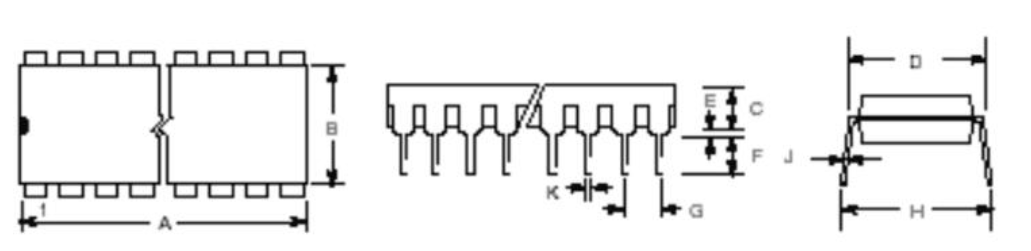

Dimensioune vum DS1302

Fabrikant vun DS1302

Maximatesch integréiert féiert déi queologesch Landschaftssportsvitresstatioune wärend der Synchonung an der Synchonescher, och Zesummenaarbecht, Kraaft, d'Technescher Kommologie, Kraaftkoschung?Dës Beräicher fosen Seamless Elektronesch Interaktiounen an optiméiert Energie Benotzung, garantéiert ofhängeg Informatiounsaustausch.D'Firma Fecht kreativ Engine

Vergläichbar Deeler

|

|

DS1302 + |

DS1307n +

|

DS1337 +

|

DS1672-2 +

|

|

Hiersteller |

Maxim integréiert |

Maxim integréiert |

Maxim integréiert |

Maxim integréiert |

|

Package / Fall |

8-Dip (0,300, 7.62mm) |

8-Dip (0,300, 7.62mm) |

8-Dip (0,300, 7.62mm) |

8-Dip (0,300, 7.62mm) |

|

Zuel vun de Pinnen |

8 |

8 |

8 |

8 |

|

Gedächtnisgréisst |

31b |

56.b |

- |

31b |

|

Interzäit |

3-Wire Serial |

I2C, 2-Drot Serien |

I2C, 2-Drot Serien |

3-Wire Serial |

|

Logesch Funktioun |

Wopp |

Wopp |

Wopp |

Wopp |

|

Liwwerreibei |

3.3 v |

5 v |

3.3 v |

3.3 v |

|

Zuel vun den Terminatiounen |

8 |

8 |

8 |

8 |

|

Mont |

Duerch Lach |

Duerch Lach |

Duerch Lach |

Duerch Lach |

Datatheet PDF

DS1302 Datasheeter

DS1302.PDFDS1302 Detailer PDF

DS1302 PDF - De.PDF

DS1302 + DATASHESS

DS1302 + .PDFDS1302 + Detailer PDF

DS1302 + PDF - De.PDF

DS1302N Dataschetten

DS1302N.PDFDS1302N Detailer PDF

DS1302n PDF - De.PDF

DS1307n + Datasheeter

DS1307n + .pdfDS1307n + Detailer PDF

DS1307n + PDF - De.PDF

DS1307n + PDF - Fr.PDF

DS1307n + PDF - ES.PDF

DS1307n + PDF - IT.PDF

DS1307n + PDF - kr.pdf

DS1337 + Dataschetten

DS1337 + .PDFDS1337 + Detailer PDF

DS1337 + PDF - De.PDF

DS1672-2 + DATASHESS

DS1672-2 + .PDFDS1672-2 + Detailer pdf

DS1672-2 + PDF - De.PDF

IWWERT ONS

Clientszefriddenheet all Kéier.Géigesäitege Vertrauen an allgemeng Interesse.

IWWERT ONS

Clientszefriddenheet all Kéier.Géigesäitege Vertrauen an allgemeng Interesse.

Funktioun Test.Déi eng Déi héchste Produite vum Site ass eisen eigentlech Engelagement vun Iech.

Waarm Artikel

- LM358 Duell Operationalverléiser iwwergräifendem Rotschléi: Pinnuts, Circuit Diagungsmageschagéier, Equemen, nëtzlech Beispiller

- Sinn cr2032 an cr2016 Austauschbar?

- D'Ënnerscheeder esp32 an esp32-S3 techneschen an Erlaabnis Analyse

- Wielt déi richteg Batterie: e Guide op Ag4, lR626, LR66, 177/376/376sw Equivalenter

- NPN vs. PNP: Wat ass den Ënnerscheed?

- BC547 Transistor Basics: Pinout, Applikatioun Circuits, Alternativ / Ergänzlech Modeller

- esp32 vs stm32: wéi ee Microcontroller ass besser fir Iech?

- Wat ass e Mosfet a wéi et funktionnéiert?

- Elektresch Relais Basis: Aarbechtsoperatioun, Aarte a Gebrauch

- PNP Transistors: Struktur, Aarbechtsinquish an Uwendung

At28C256 Page PALLEREL EEPROM VUM VERHËNNERT Ruffer

At28C256 Page PALLEREL EEPROM VUM VERHËNNERT Ruffer

2024-11-09

Äre Guide an ad8479 Präzisiounsverdeelung Amplifier

Äre Guide an ad8479 Präzisiounsverdeelung Amplifier

2024-11-09

Oft gestallten Froen [FAQ]

1. Wéi geet d'DS1302 Funktioun?

Den DS1302 Chip kombinéiert eng Echtzäit Auer / Kalenner Feature mat zousätzlech Erënnerung, maacht et kapabel detailléiert Zäitdaten ze liwweren.Seng semlos Integratioun mat Mikroprocessors Apparater fir Zäit sensibel Aufgaben mat Genauegkeet ze managen.Dës Fäegkeet gëtt héich ugesinn an Systemer, déi präventéierend Timing erfuerderen an Daten aloggen, sou wéi déi an industriellen Domainen oder verschidde Konsumenten Elektronik.Vun Ënnerweisung Affekleetodabilitéit mat Erënnerungen, den Chip bitt den Chip zur Synchon behält sech an säin Ofhängt an den Ofsabilitéit an den Design.

2. Ass den DS1302 kompatibel mat I2C?

Den DS1302 ass net als I2C Apparat entworf, awer et iwwergeet a effizient Leeschtung, dauernd bis zu fënnef Joer, wann Dir vun enger 3V Lithium Batterie gemaach hutt.Et benotzt eng rengem Herrfanke Sozial Kommunikatiounspartier vun I2C, mat engem Fokus op der Longerityverbrauch.Systeming Systemer mat dësem Chip involvéiert en eenzegaartegen eenzegaartege Kommunikatiouns Stil-Distinct vun der Mainstream Protokoller ze bidden, ouni Komunitéit ouni Komplexitéit.

3. Wéi geet den DS1302 anescht vun der DS1307?

Den DS130 an Ds130 ënnerscheet sech haaptsächlech a Pullfaktatioune vu Padeau Fricht an besonnesch Zoitateien auszegoen.Dës Differenzen begräifen;Mir sinn bei ënnerschiddleche Chips an engem jealen Ververstännegen an elektresch Verloschter gemaach.Dës subtil Differen, déi de Wäert vun den Ukloe Circuit Designen zoumaachen, fir all Komplott vun der Crafvention eventueller selbstverständlech Systemer ergänzen.

4. Wat ass en RTC?

Eng Echtzäit Auer (RTC) Funktiounen als Timeseeping Microchip an Systemer, déi vun enger Batterie erakommen, garantéiert eng kontinuéierlech Zäit Daten fir Computapplikatioune fir Computerapparatatiounen.Den TRTC Design erlaabt et zu Genauegkeet vun der Erlaabnes vun der Haaptkraaftquell ze behalen, verbessert d'Effort an der Apparagement iwwer eng breet Palette vun Uwendungen.Seng Bedeitung gëtt kloer am Szenarie wou temporär Konsistenz noutwendeg ass, verlaangt de Geräter d'Fäegkeet ze bleiwen fir zouverléisseg ze bleiwen ouni op extern Timing Timing ze bleiwen.

5. Firwat ass en RTC benotzt?

Rertces si fir eng engëlschter Zäiten oder verschiddene Systemer wéi diigantesch FlockstAen, woufir néideg Zäitstamellen sinn.Hir Roll ass am meeschte protokolléiert an Astellungen déi strikt Zäit Koordinatioun verlaangen.Offiziell Zäit Gestioun Boots System Leeschtung, ënnerstëtzt d'Ergänzung vun der Fäegkeet ofhängeg vu Präzis, wéi d'Datetomung a wëssenschaftleche Fuerschung an der Finanztrunptiounen.Schlussderul soll d'keng Fäegkeet fir d'Verkuffegung an d'Technologie vun der Technologie zréckbauen, refuséiert sou richteg Deel vun der RTCsform

Hotender.

AC0603JRNPOYBN150

AC0603JRNPOYBN150 VI-26L-EY

VI-26L-EY L6226Q

L6226Q AD9878BSTZ

AD9878BSTZ GJM0335C1E7R9DB01J

GJM0335C1E7R9DB01J IDT72V7230L10BBG

IDT72V7230L10BBG GRM0336R1E6R1DD01D

GRM0336R1E6R1DD01D LTM2882IY-3#PBF

LTM2882IY-3#PBF GRM1557U1H8R5DZ01D

GRM1557U1H8R5DZ01D VI-2W4-CV

VI-2W4-CV

- VE-2T2-CW

- 08055A271KAT4A

- CGA4C2NP01H392J060AA

- T491C156K035ZT7280

- ISL6401CBZ-T

- VI-262-IW

- GRM033R61C123KE84D

- XRA1207IG24-F

- NC7SZ00M5X

- 12065A1R2CAT2A

- ISL43141IVZ

- ATSAM3S4CA-AU

- 12063C684KAZ2A

- STTH8L06G

- C3216Y5V0J476Z/8

- 06033C153JAT2A

- LM5175PWPR

- S94810504

- AT89C51RD2-CL

- M3087LFYBGP

- M36L0R7060T2ZAQ

- MC145220FR2

- PPC405EP-3LB333C

- PW2300B-10L

- SCY99053

- UPD703273YGC-362-8EA

- UPD75518GF-233-3B9

- ADR395BUJZ

- CM6800T+XISTR

- P45278003117

- TK63133BCB-G

- UAC3556B-QI-G10

- VSPM300RQCSV100

- MM74HC595

- ATMXT640T-CCUR048

- BCM53286MIPB

- PC87366-IBM

- HYUF6404E-D551

- L-APP345E-3-2A13-DB